3312 Spanning Tree Algorithms 3313 Shortest Path Algorithms. 1 Variation tolerance in useful skew design 2 Link insertion for buffered clock nets 3 Methodology and algorithms for.

Clock Tree Synthesis Cts Ivlsi

This dissertation addresses variation and power issues in the design of current and potential future CDN.

. Reg-A is flop inside block that is sending data through PORT outside the block. There are number of algorithms to build the clock tree. To avoid the clock skew FSTM constructs a binary tree such that for each internal vertex of the tree the cardinality of its sub-trees are balanced and the distances to its children are equal.

The book is a core reference for graduate students and CAD professionals. An extensive bibliography is provided which is useful for finding advanced material on a topic. Of buffer levels NDR Nondefault routing rules because clock nets are more prone to cross-talk effect Routing metal layers used for clocks.

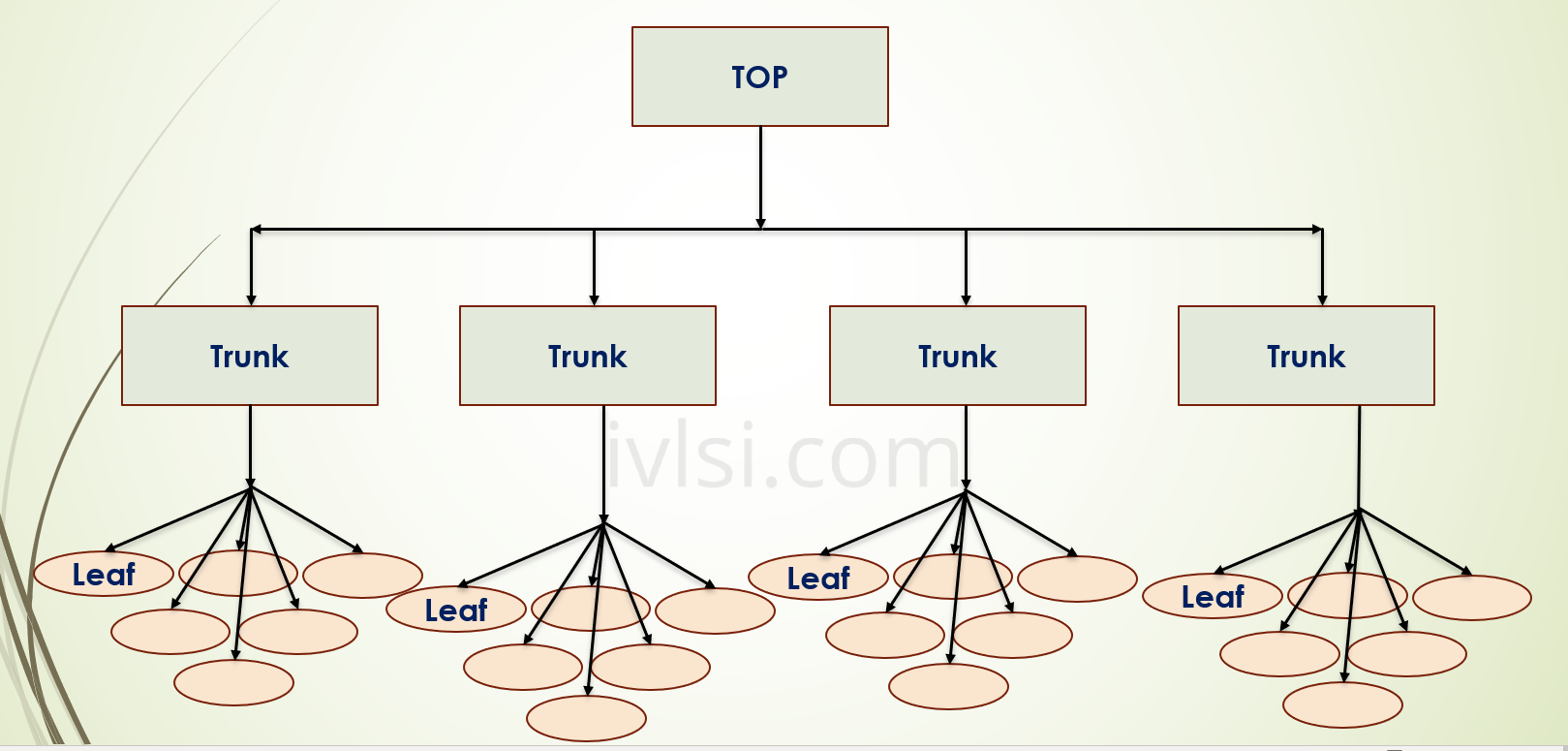

Leafs of the tree being analogous to the sequential devices being triggered by the clock signal and the root being analogous to the clock source. H g 4 11 Electronic Design Automation EDA. Figure 1 shows a scenario where it helps to define a virtual clock.

In recent times in order to compete the clock tree balancing we use H tree algorithm. CTS starting point is clock source and CTS ending point is clock pins of sequential cells. Answer 1 of 2.

It has been shown by Srikanth and Toueg that in a system of nodes Algorithm 1 in cooperation with the consistent broadcast primitive of Algorithm 2 solves the clock synchronization problem even in the presence of up to Byzantine faulty nodes if the conditions hold that i the local clocks maximum drift rate is known and bounded by ii message end-to-end delays are within a. It is used as a reference to constrain the interface pins by. Pev Words and muhipliers multiplication VLSI multipliers 4-2 multipliers 4-2 trees iterative VLSI Clocking.

Since it is a synchronous signal we can assume it to be captured by a flop Reg-B sitting outside the block. Multiplexed drive Cycle through N displays at a high rate few kHz to result in a persistent display N7 pins drivers for N displays Display blanking to avoid wrong digit flickering. 331 Graph Algorithms.

In earlier days it was considered that. The research detailed in this work presents algo-rithmic techniques for the following problems. Clock signal is the most fundamental signal for any digital circuit.

12 VLSI Design Flow 13 VLSI Design Styles 14 Layout Layers and Design Rules 15 Physical Design Optimizations 16 Algorithms and Complexity 17 Graph Theory Terminology 18 Common EDA Terminology. A look-up table based buffer sizing approach is developed for variation tolerance improvement. Presents a new algorithm called FSTM feasible segment tree method for the clock net routing of high performance VLSI designs.

Algorithm steps for the H-Tree. Every clock sink should get the clock at the same time. Before CTS all clock pins are driven by a single clock source.

Find out all the flops present. For CAD professionals the material presents a balance of theory and practice. Now within the block the path to PORT can be timed by specifying output delay for.

Interesting several high-performance rounding algorithms compatible with IEEE standard 754 for binary floating-point arithmetic have also been developed. Gating technique on some synchronous digital design like ALU Arithmetic logical unit and FIFOfirst in first out etc. A virtual clock can be defined as a clock without any source or in other words a virtual clock is a clock that has been defined but has not been associated with any pinport-.

3315 Min-Cut and Max-Cut Algorithms. We implemented Useful-Skew Tree UST algorithm which is based on the deferred-merge embedding DME paradigm as the clock layout synthesis engine. Switching activity is high since clock toggles constantly.

During timing analysis you need to check timing on IO ports as well as they actually come from a flop in some other block to current block in which you are analyzing timing. 33 Basic Algorithms. A dual-MZ blockage handling technique is developed for buffer location distribution and.

For solving large complex problems. Clock tree DRC max Tran max cap max fan-out max no. So to model the clock latency and clock relationship in other block we need virtual clock.

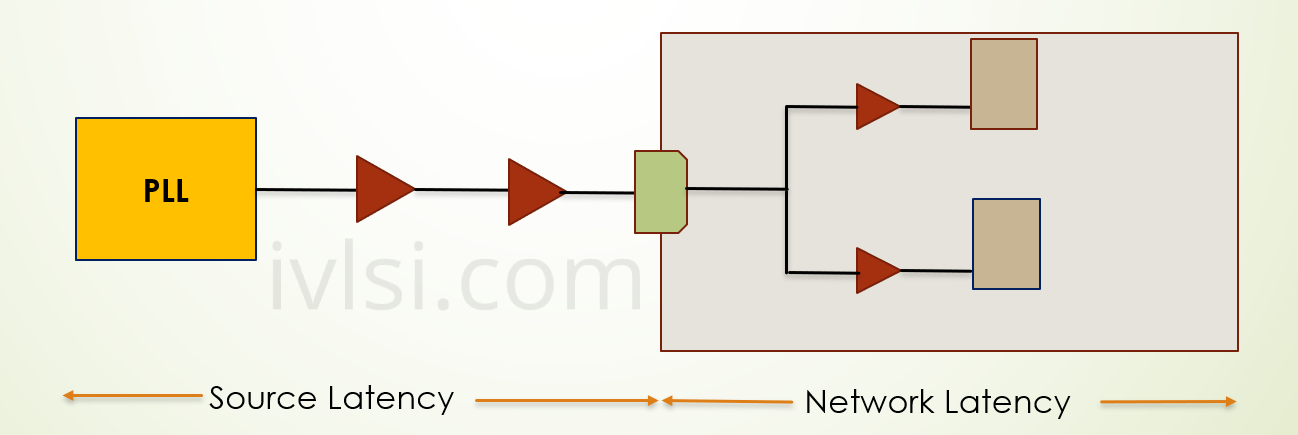

Clock power consumption depends on switching activity and wire length. Lets go into the details of H Tree algorithm. The goal of clock tree synthesis is to get the skew in the design to be close to zero.

But the size and the complexity of the VLSI design has increased over time hence some of the problems can be solved using partitioning techniques. Clock virtual clock. The source of clock and all the sinks where the clock is going to feed all sink pins.

For students concepts and algorithms are presented in an intuitive manner. Clock Tree Synthesis g. The partitioning methodology proved to be very useful in solving the VLSI design automation problems occurring in every stage of the IC de sign process.

An iterative buffer insertion technique is developed for delay balancing and capacitance reduction. 3316 Steiner Tree Algorithms. A clock signal originates from a clock sourceThere may be designs with a single clock source while some designs have multiple clock sources.

Clock period to improve theperformance of synchronousdigital circuitWe implementedUseful-Skew Tree UST algorithm which is based on thedeferred-merge embedding DME paradigm as the clock layout synthesis engine. It does not physically exist in the design but it does exist in the memory. A dual-MST perfect matching algorithm is developed for symmetric clock tree construction.

Find out the center of all the flops. 3311 Graph Search Algorithms. 3314 Matching Algorithms.

H g 8 13 VLSI Design Styles Layer Palette Mouse Buttons Bar Layout Windows. The algorithm to design an optimal clock-schedule was given. Power Clock is a major power consumer in your design.

Enable only when digit input is stable Larger peak current sqrtN to preserve brightness. Clock gating synchronous circuit VLSI EDA DSP. The synthesis module is integrated with the UTM in-house design graph accelerator to.

CTS is the process of insertion of buffers or inverters along the clock paths of ASIC design in order to achieve zerominimum skew or balanced skew. In this paper we propose a clock-tree routing algorithm that realizes a given clock-schedule using the Elmore-delay model. The clock signal is distributed in the design in the form of a tree.

Virtual clock is used to time interface paths.

Clocking Strategies In Vlsi Systems Electrical And Electronic

Cts Part I Vlsi Physical Design For Freshers

Clock Tree Synthesis Cts Ivlsi

Clock Tree Routing Algorithms Vlsi Physical Design For Freshers

0 Comments